# Intel® Xeon® Processor E7-8800/4800/2800 Product Families

**Datasheet Volume 1 of 2**

April 2011

Reference Number: 325119-001

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL<sup>®</sup> PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

The Intel® Xeon® Processor E7-8800/4800/2800 Product Families may contain design defects or errors known as errata, which may cause the product to deviate from published specifications. Current characterized errata are available upon request.

Throughout this document, Intel® Xeon® Processor E7-8800/4800/2800 Product Families will be referred to as the Intel® Xeon® E7-8800/4800/2800 Product Families Processor when used in referring to a singular processor.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com/design/literature.htm

64-bit computing on Intel architecture requires a computer system with a processor, chipset, BIOS, operating system, device drivers and applications enabled for Intel<sup>®</sup> 64 architecture. Performance will vary depending on your hardware and software configurations. Consult with your system vendor for more information. For more information, visit <a href="http://www.intel.com/info/em64t">http://www.intel.com/info/em64t</a>.

Intel® AES-NI requires a computer system with an AES-NI enabled processor, as well as non-Intel software to execute the instructions in the correct sequence. AES-NI is available on select Intel® processors. For availability, consult your reseller or system manufacturer. For more information, see http://software.intel.com/en-us/articles/intel-advanced-encryption-standard-instructions-aes-ni/

Enhanced Intel SpeedStep Technology: See the Processor Spec Finder at http://ark.intel.com or contact your Intel representative for more information.

Enabling Execute Disable Bit functionality requires a PC with a processor with Execute Disable Bit capability and a supporting operating system. Check with your PC manufacturer to determine whether your system delivers this functionality. For more information, visit http://www.intel.com/technology/xdbit/index.htm

Intel® Virtualization Technology requires a computer system with an enabled Intel® processor, BIOS, virtual machine monitor (VMM) and for some uses, certain computer system software enabled for it. Functionality, performance or other benefits will vary depending on hardware and software configurations and may require a BIOS update. Software applications may not be compatible with all operating systems. Please check with your application vendor.

Intel processor numbers are not a measure of performance. Processor numbers differentiate features within each processor family, not across different processor families. Go to: http://www.intel.com/products/processor\_number

Intel® Turbo Boost Technology requires a PC with a processor with Intel® Turbo Boost Technology capability. Intel Turbo Boost Technology performance varies depending on hardware, software and system configuration. Consult your PC manufacturer on whether your system delivers Intel Turbo Boost Technology. For more information, visit <a href="http://www.intel.com/technology/turboboost">http://www.intel.com/technology/turboboost</a>

Intel, Intel Xeon, the Intel logo and Intel SpeedStep are trademarks or registered trademarks of Intel Corporation in the United States and other countries.

$\rm I^2C$  is a two-wire communications bus/protocol developed by Philips. SMBus is a subset of the  $\rm I^2C$  bus/protocol and was developed by Intel. Implementations of the  $\rm I^2C$  bus/protocol may require licenses from various entities, including Philips Electronics N.V. and North American Philips Corporation.

\*Other names and brands may be claimed as the property of others.

Copyright © 2011, Intel Corporation. All Rights Reserved.

# Contents

| 1 | Intro | duction            | ۱                                                                                       | 9   |

|---|-------|--------------------|-----------------------------------------------------------------------------------------|-----|

|   | 1.1   |                    | ology                                                                                   |     |

|   | 1.2   |                    | nces                                                                                    |     |

|   | 1.3   |                    | of Data                                                                                 |     |

|   | 1.4   | Statem             | ent of Volatility                                                                       | 11  |

| 2 | Elect | rical Sp           | ecifications                                                                            | 13  |

|   | 2.1   | Process            | sor Maximum Ratings                                                                     | 13  |

|   | 2.2   | Socket             | Voltage Identification                                                                  | 14  |

|   | 2.3   |                    | Groups                                                                                  |     |

|   | 2.4   |                    | sor DC Specifications                                                                   | 21  |

|   | 2.5   | Intel <sup>®</sup> | QPI and Intel <sup>®</sup> Scalable Memory Interconnect (Intel <sup>®</sup> SMI)        | 20  |

|   |       |                    | ce Differential Signaling                                                               |     |

|   |       | 2.5.1<br>2.5.2     | Intel QPI Signaling Specifications                                                      |     |

|   |       | 2.5.2              | Intel QPI Electrical Specifications<br>Intel SMI Signaling Specifications               |     |

|   |       | 2.5.3              | Intel SMI Signaling Specifications<br>Intel SMI Transmitter and Receiver Specifications |     |

|   | 2.6   |                    | m Environmental Control Interface (PECI) DC Specifications                              |     |

|   | 2.0   | 2.6.1              | DC Characteristics                                                                      |     |

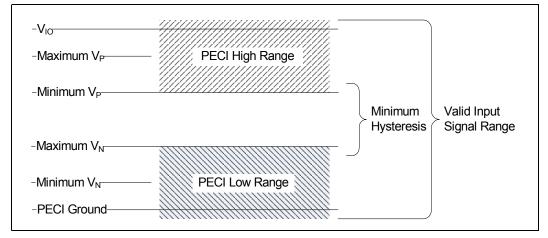

|   |       | 2.6.2              | Input Device Hysteresis                                                                 |     |

|   | 2.7   |                    | ecifications                                                                            |     |

|   | 2.8   |                    | cifications                                                                             |     |

|   | 2.9   |                    | sor AC Timing Waveforms                                                                 |     |

|   | 2.10  | Flexible           | e Motherboard Guidelines                                                                | 55  |

|   | 2.11  |                    | ed (RSVD) or Unused Signals                                                             |     |

|   | 2.12  |                    | ccess Port Connection                                                                   |     |

|   | 2.13  |                    | Processors                                                                              |     |

|   | 2.14  | Process            | sor SPD Interface                                                                       | 55  |

| 3 | Proce | essor Pa           | ackage Mechanical Specifications                                                        | 57  |

|   | 3.1   |                    | e Mechanical Specifications                                                             |     |

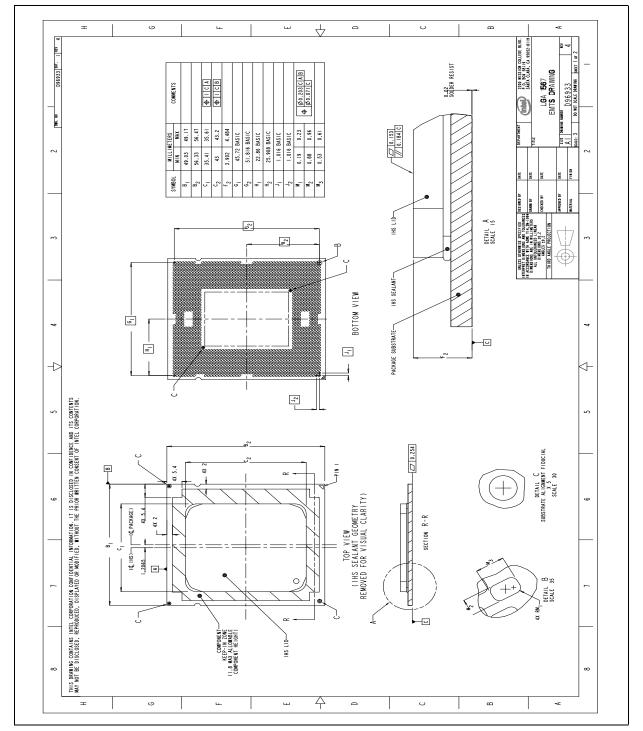

|   |       | 3.1.1              | Package Mechanical Drawing                                                              | 58  |

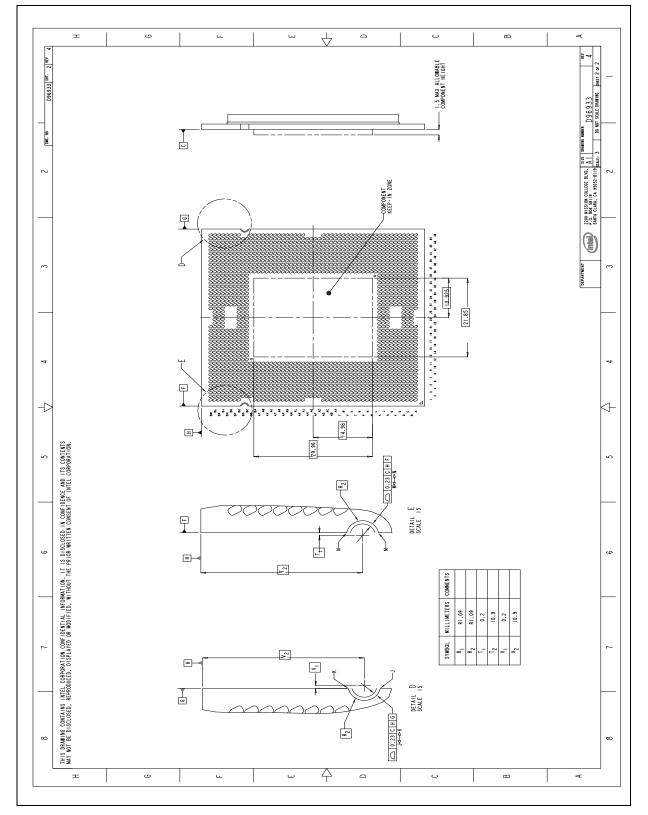

|   |       | 3.1.2              | Processor Component Keep-Out Zones                                                      |     |

|   |       | 3.1.3              | Package Loading Specifications                                                          |     |

|   |       | 3.1.4              | Package Handling Guidelines                                                             |     |

|   |       | 3.1.5              | Package Insertion Specifications                                                        |     |

|   |       | 3.1.6              | Processor Mass Specification                                                            |     |

|   |       | 3.1.7              | Processor Materials                                                                     |     |

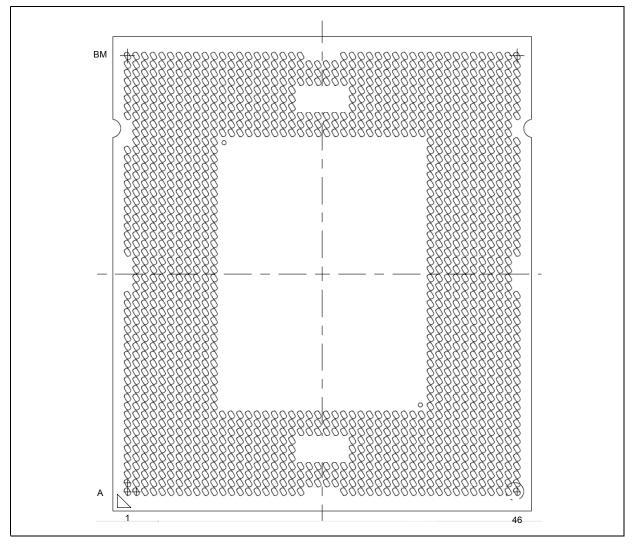

|   |       | 3.1.8<br>3.1.9     | Processor Markings<br>Processor Land Coordinates                                        |     |

|   |       |                    |                                                                                         |     |

| 4 |       |                    |                                                                                         |     |

|   | 4.1   |                    | sor Package Bottom Land Assignments                                                     |     |

|   |       | 4.1.1              | Processor Pin List, Sorted by Socket Name                                               |     |

|   |       | 4.1.2              | Processor Pin List, Sorted by Land Number                                               | 85  |

| 5 | Signa | l Defin            | itions 1                                                                                | 105 |

| 6 | Therr | nal Spe            | ecifications                                                                            | 11  |

|   | 6.1   | Packag             | e Thermal Specifications 1                                                              | 11  |

|   |       | 6.1.1              | Thermal Specifications 1                                                                | 11  |

|   |       | 6.1.2              | Thermal Metrology 1                                                                     |     |

|   | 6.2   |                    | sor Thermal Features 1                                                                  |     |

|   |       | 6.2.1              | Thermal Monitor Features 1                                                              | 18  |

|   |       | 6.2.2              | Intel <sup>®</sup> Thermal Monitor 1 1                                                  | 18  |

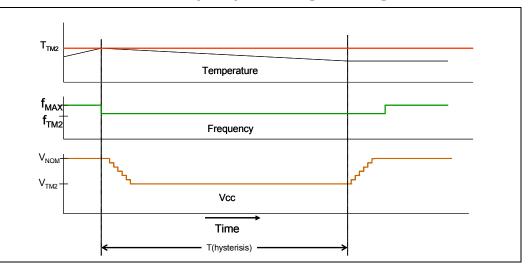

|   |       | 6.2.3    | Intel Thermal Monitor 2                               | 118 |

|---|-------|----------|-------------------------------------------------------|-----|

|   |       | 6.2.4    | On-Demand Mode                                        | 119 |

|   |       | 6.2.5    | PROCHOT_N Signal                                      |     |

|   |       | 6.2.6    | FORCE_PR_N Signal                                     | 120 |

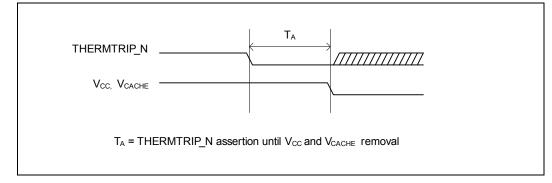

|   |       | 6.2.7    | THERMTRIP N Signal                                    | 121 |

|   |       | 6.2.8    | THERMALERT N Signal                                   | 121 |

|   | 6.3   | Platforr | m Environment Control Interface (PECI)                |     |

|   |       | 6.3.1    | PECI Client Capabilities                              |     |

|   |       | 6.3.2    | Client Command Suite                                  |     |

|   |       | 6.3.3    | Multi-Domain Commands                                 | 138 |

|   |       | 6.3.4    | Client Responses                                      | 138 |

|   |       | 6.3.5    | Originator Responses                                  |     |

|   |       | 6.3.6    | Temperature Data                                      | 140 |

|   |       | 6.3.7    | Client Management                                     | 141 |

| 7 | Fostu | roc      | -                                                     | 1/5 |

| / | 7.1   |          | uction                                                |     |

|   | 7.1   |          | Control and Low Power States                          | -   |

|   | 1.2   | 7.2.1    | Processor C-State Power Specifications                |     |

|   | 7.3   |          | nd Access to Processor Information ROM via SMBus      |     |

|   | 7.5   | 7.3.1    | Processor Information ROM                             |     |

|   |       | 7.3.1    | Scratch EEPROM                                        |     |

|   |       | 7.3.2    | PIROM and Scratch EEPROM Supported SMBus Transactions |     |

|   | 7.4   |          | Memory Component Addressing                           |     |

|   | 7.5   |          | ng Data in the PIROM                                  |     |

|   | 7.5   | 7.5.1    | Header                                                |     |

|   |       | 7.5.2    | Processor Data                                        |     |

|   |       | 7.5.3    | Processor Core Data                                   | -   |

|   |       | 7.5.4    | Processor Uncore Data                                 |     |

|   |       | 7.5.5    | Package Data                                          |     |

|   |       | 7.5.6    | Part Number Data                                      |     |

|   |       | 7.5.7    | Thermal Reference Data                                |     |

|   |       | 7.5.8    | Feature Data                                          |     |

|   |       | 7.5.9    | Other Data                                            |     |

|   |       |          | Checksums                                             |     |

|   | _     |          |                                                       |     |

| 8 |       | -        | Specifications                                        |     |

|   | 8.1   | 5        | nalyzer Interface                                     |     |

|   |       | 8.1.1    | Mechanical Considerations                             |     |

|   |       | 8.1.2    | Electrical Considerations                             | 173 |

# **Figures**

| 2-1  | VCC Static and Transient Tolerance                                       | 24  |

|------|--------------------------------------------------------------------------|-----|

| 2-2  | Vcache Static and Transient Tolerance                                    | 25  |

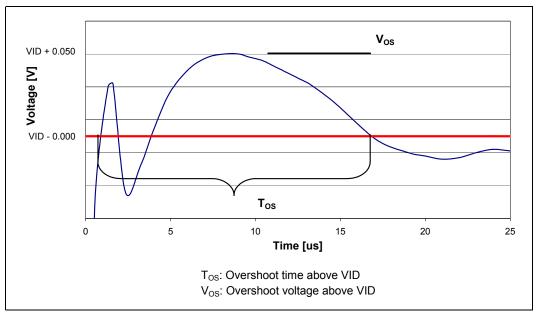

| 2-3  | Overshoot Example Waveform                                               | 26  |

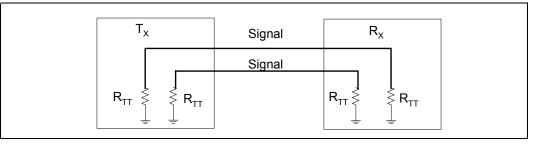

| 2-4  | Active ODT for a Differential Link Example                               | 26  |

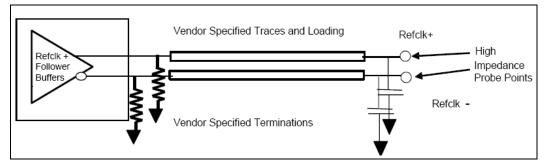

| 2-5  | Validation Topology for Testing Specifications of the Reference Clock    | 27  |

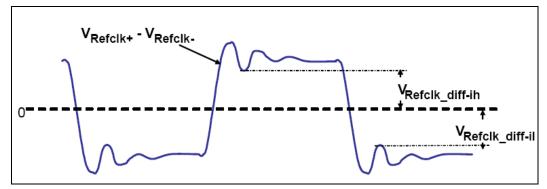

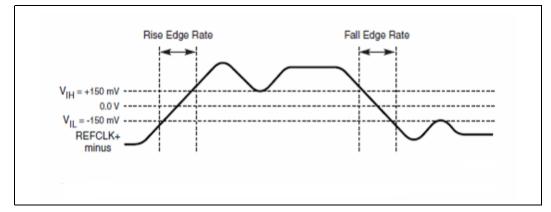

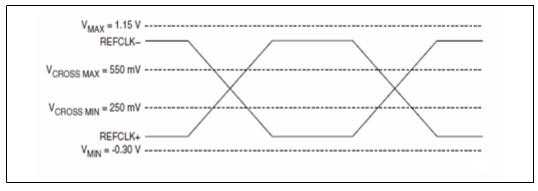

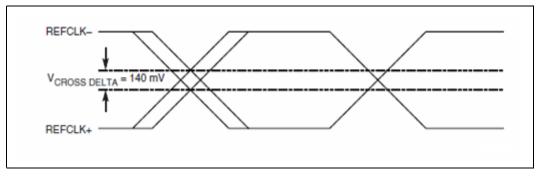

| 2-6  | Differential Waveform Measurement Points                                 |     |

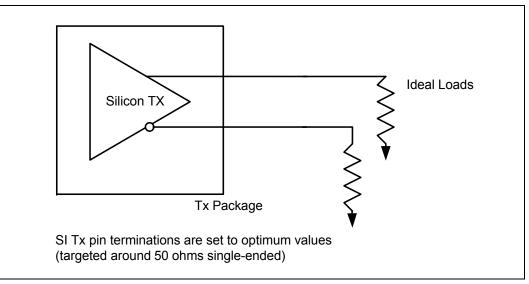

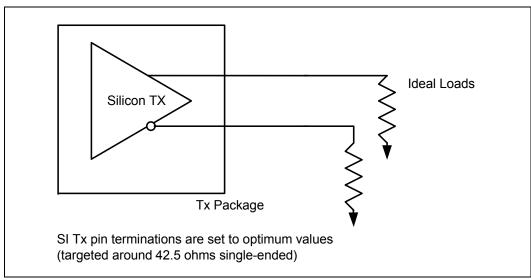

| 2-7  | Setup for Validating Standalone Tx Voltage and Timing Parameters         |     |

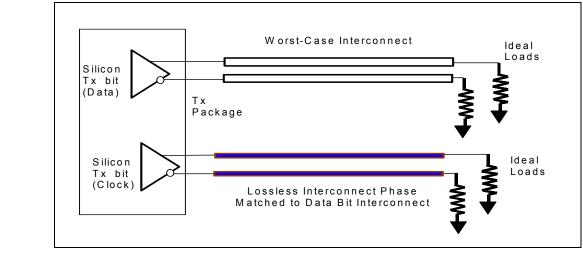

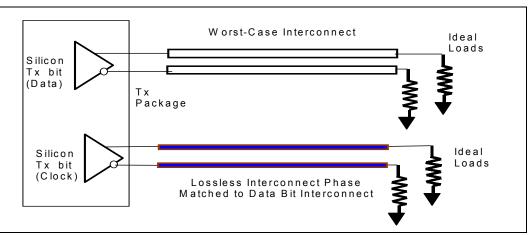

| 2-8  | Setup for Validating Tx + Worst-Case Interconnect Specifications         |     |

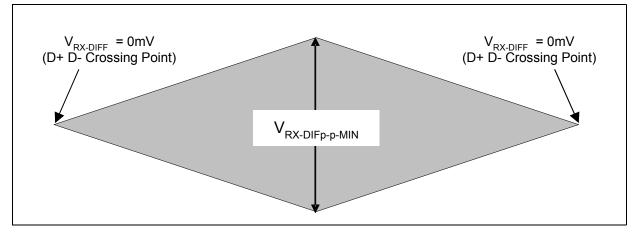

| 2-9  | Required Receiver Input Eye (Differential) Showing Minimum Voltage Specs |     |

| 2-10 |                                                                          |     |

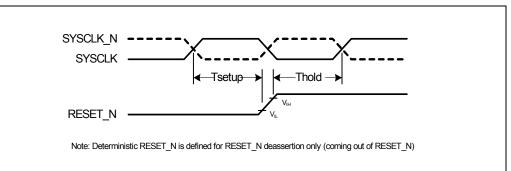

| 2-11 | RESET_N SEtup/Hold Time for Deterministic RESET_N Deassertion            |     |

| 2-12 |                                                                          |     |

| 2-13 |                                                                          |     |

| 2-14 | •                                                                        |     |

| 2-15 | -                                                                        |     |

| 2-16 |                                                                          |     |

| 2-17 | -                                                                        |     |

| 2-18 |                                                                          | 40  |

| 2 10 | Waveform                                                                 | 49  |

| 2-19 |                                                                          |     |

| 2 17 | Standalone TX Voltage and Timing Parameters                              | 49  |

| 2-20 |                                                                          |     |

| 2 20 | TX + Worst-Case Interconnect Specifications                              | 50  |

| 2-21 |                                                                          |     |

| 2-22 |                                                                          |     |

| 2-23 |                                                                          |     |

| 2-24 |                                                                          |     |

| 2-25 | -                                                                        |     |

| 2-26 |                                                                          |     |

| 2-27 | -                                                                        |     |

| 2-28 |                                                                          |     |

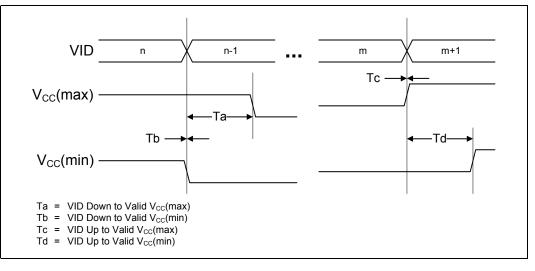

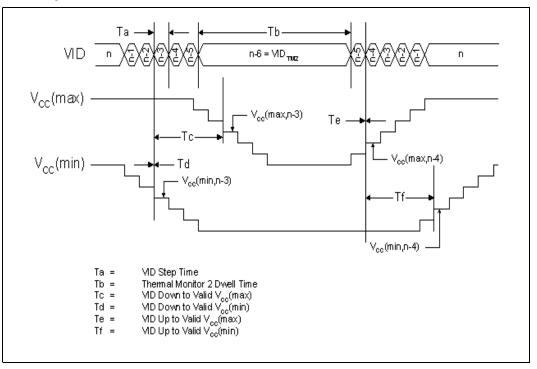

| 2-29 | VID Step Times and Vcc Waveforms                                         |     |

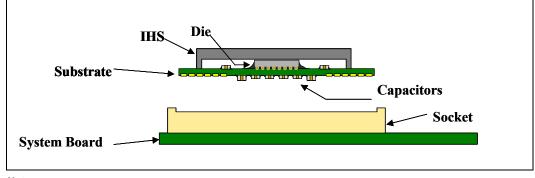

| 3-1  | Processor Package Assembly Sketch                                        |     |

| 3-2  | Processor Package Drawing (Sheet 1 of 2)                                 |     |

| 3-3  | Processor Package Drawing (Sheet 2 of 2)                                 |     |

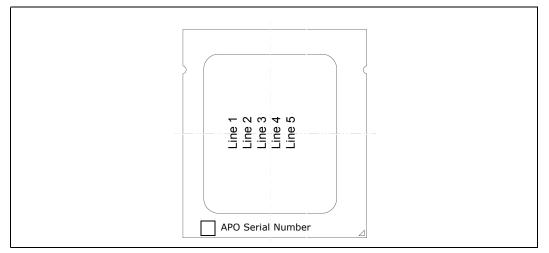

| 3-4  | Processor Top-Side Markings                                              |     |

| 3-5  | Processor Land Coordinates and Quadrants, Top View                       |     |

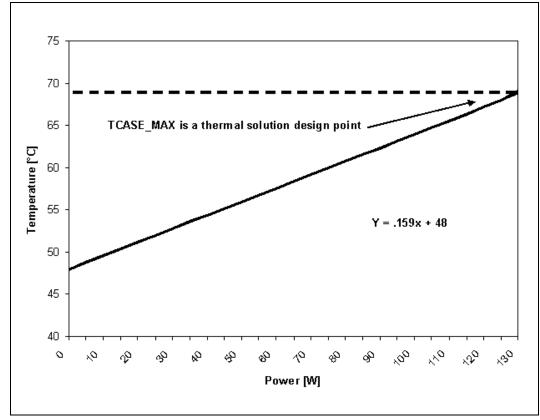

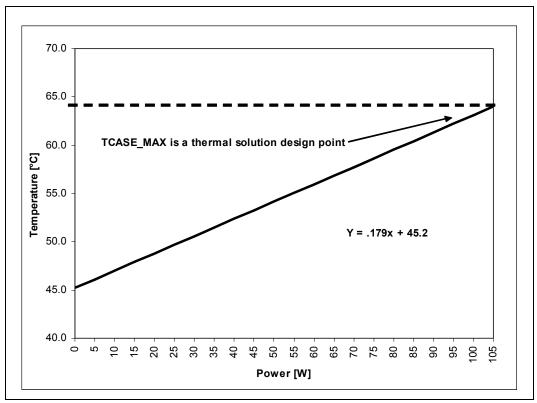

| 6-1  | 130W TDP Processor Thermal Profile                                       |     |

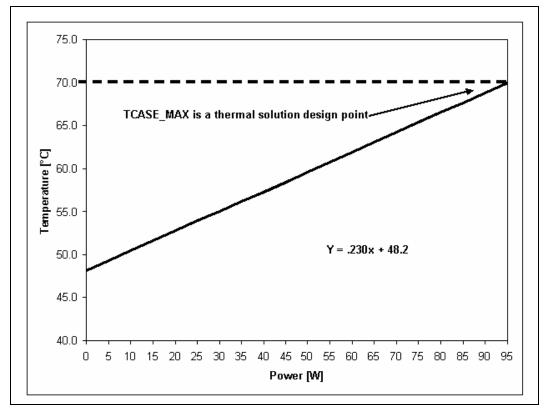

| 6-2  | 105W TDP Processor Thermal Profile                                       |     |

| 6-3  | 95W TDP Processor Thermal Profile                                        |     |

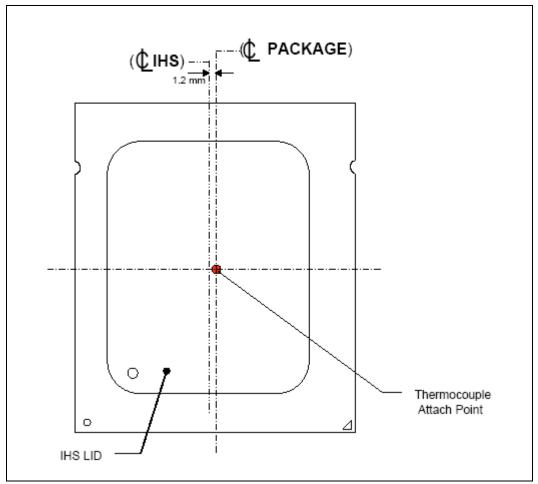

| 6-4  | Case Temperature (TCASE) Measurement Location                            |     |

| 6-5  | Intel® Thermal Monitor 2 Frequency and Voltage Ordering                  |     |

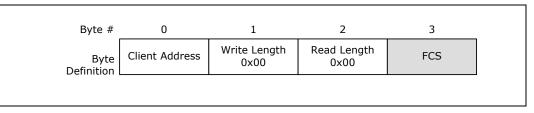

| 6-6  | Ping()                                                                   |     |

| 6-7  | Ping() Example                                                           |     |

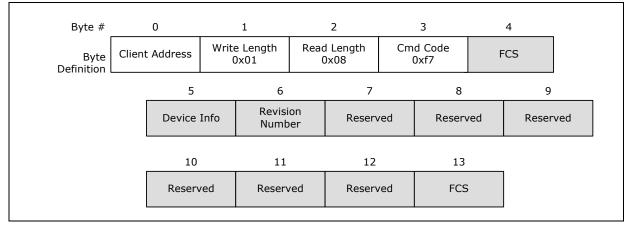

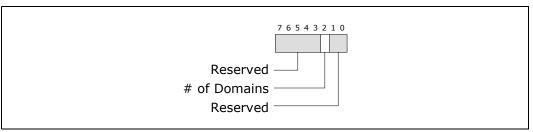

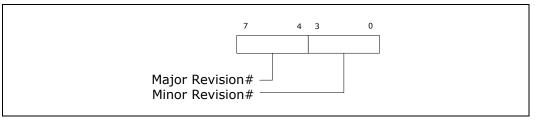

| 6-8  | GetDIB()                                                                 |     |

| 6-9  | Device Info Field Definition                                             |     |

| 6-10 | Revision Number Definition                                               |     |

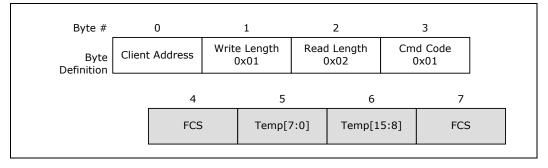

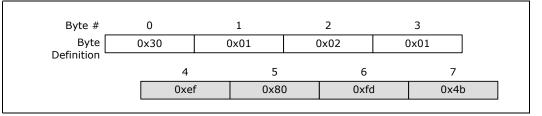

| 6-11 | GetTemp()                                                                |     |

| 6-12 |                                                                          |     |

| 6-12 |                                                                          |     |

|      |                                                                          |     |

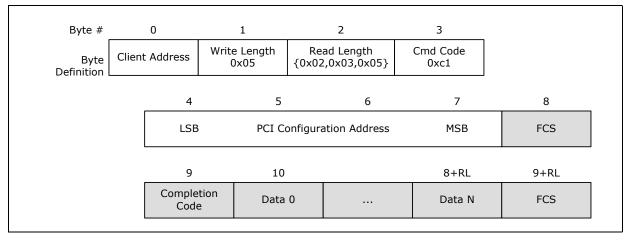

| 6-14 | PCIConfigRd()                                                            | 171 |

| PCIConfigWr()                                                                         |                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

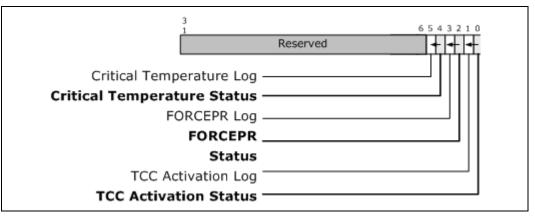

| Thermal Status Word                                                                   |                                                                                                                                                                                                                                                                                                                                                                                   |

| Thermal Data Configuration Register                                                   |                                                                                                                                                                                                                                                                                                                                                                                   |

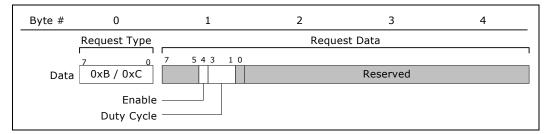

| ACPI T-state Throttling Control Read / Write Definition                               |                                                                                                                                                                                                                                                                                                                                                                                   |

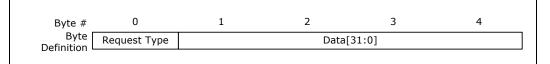

| MbxSend() Command Data Format                                                         |                                                                                                                                                                                                                                                                                                                                                                                   |

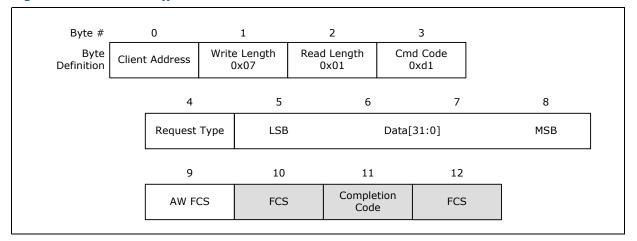

| MbxSend()                                                                             |                                                                                                                                                                                                                                                                                                                                                                                   |

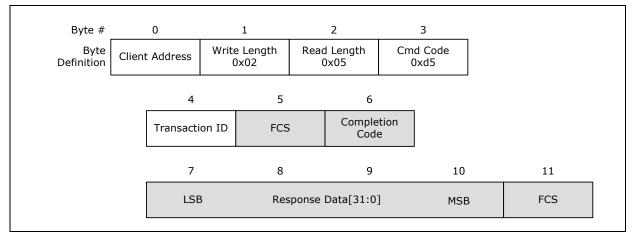

| MbxGet()                                                                              |                                                                                                                                                                                                                                                                                                                                                                                   |

| Temperature Sensor Data Format                                                        |                                                                                                                                                                                                                                                                                                                                                                                   |

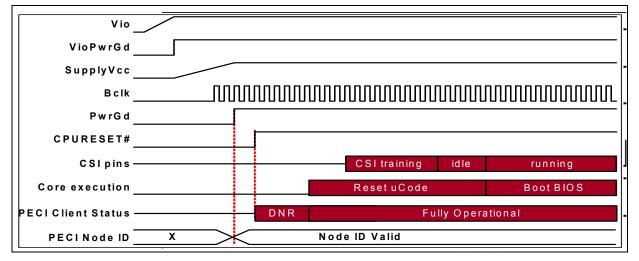

| PECI Power-up Timeline                                                                |                                                                                                                                                                                                                                                                                                                                                                                   |

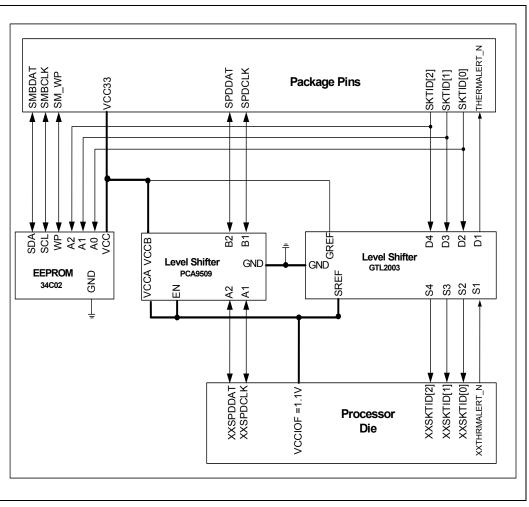

| Logical Schematic of Intel <sup>®</sup> Xeon <sup>®</sup> Processor E7-8800/4800/2800 |                                                                                                                                                                                                                                                                                                                                                                                   |

| Product Families Package                                                              | 145                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                       | PCIConfigWr()<br>Thermal Status Word<br>Thermal Data Configuration Register<br>ACPI T-state Throttling Control Read / Write Definition<br>MbxSend() Command Data Format<br>MbxSend()<br>MbxGet()<br>Temperature Sensor Data Format<br>PECI Power-up Timeline<br>Logical Schematic of Intel <sup>®</sup> Xeon <sup>®</sup> Processor E7-8800/4800/2800<br>Product Families Package |

# **Tables**

| 1-1  | References                                                           |

|------|----------------------------------------------------------------------|

| 2-1  | Processor Absolute Maximum Ratings                                   |

| 2-2  | Voltage Identification Definition15                                  |

| 2-3  | Signal Groups                                                        |

| 2-4  | Signals with RTT21                                                   |

| 2-5  | Voltage and Current Specifications                                   |

| 2-6  | Processor Vcc Static and Transient Tolerance23                       |

| 2-7  | Processor VccCache Static and Transient Tolerance24                  |

| 2-8  | VCC and Vcache overshoot Specification25                             |

| 2-9  | System Clock Specifications27                                        |

| 2-10 | Link Speed Independent Specifications                                |

| 2-11 | Clock Frequency Table                                                |

| 2-12 | Parameter Values for Intel® QPI Phy1 Channel at 1/4 RefClk Frequency |

| 2-13 | Parameter Values for Intel QPI Channel at 4.8 GT/s32                 |

| 2-14 | Parameter Values for Intel QPI at 6.4 GT/s33                         |

| 2-15 | Parameter Values for Intel SMI at 6.4 GT/s and lower35               |

| 2-16 | PLL Specification for TX and RX                                      |

| 2-17 | Transmitter Voltage Swing                                            |

| 2-18 | Transmitter De-emphasis (Swing Setting 110: Large)37                 |

| 2-19 | Transmitter De-emphasis (Swing Setting 100: Medium)37                |

| 2-20 | Transmitter De-emphasis (Swing Setting 010: Small)37                 |

| 2-21 | Summary of Differential Transmitter Output Specifications            |

| 2-22 | Summary of Differential Receiver Input Specifications                |

| 2-23 | PECI DC Electrical Limits41                                          |

| 2-24 | TAP, Strap Pins, Error, Powerup, RESET, Thermal, VID Signal Group DC |

|      | Specifications                                                       |

| 2-25 | Miscellaneous DC Specifications43                                    |

| 2-26 | System Reference Clock AC Specifications43                           |

| 2-27 | Miscellaneous GTL AC Specifications44                                |

| 2-28 | VID Signal Group AC Specifications45                                 |

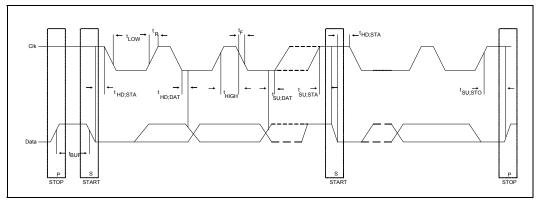

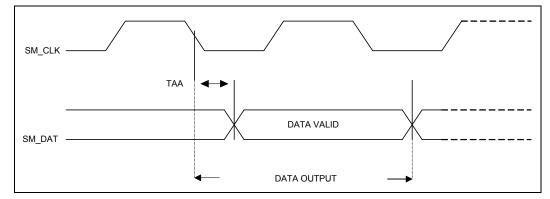

| 2-29 | SMBus and SPDBus Signal Group AC Timing Specifications46             |

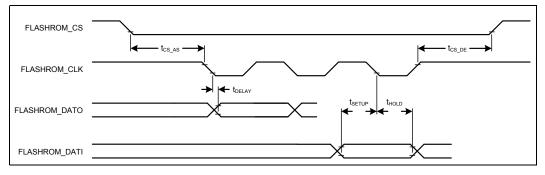

| 2-30 | FLASHROM Signal Group AC Timing Specifications47                     |

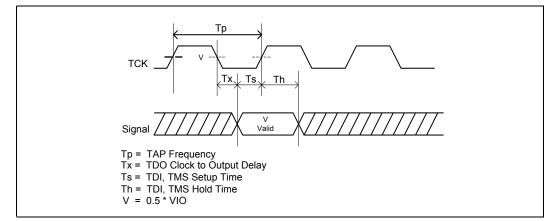

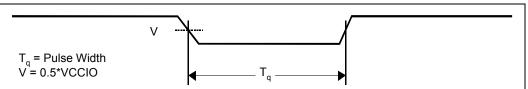

| 2-31 | TAP Signal Group AC Timing Specifications    48                      |

| 3-1  | Processor Loading Specifications                                     |

| 3-2  | Package Handling Guidelines61                                        |

| 3-3  | Processor Materials62                                                |

| 3-4  | Mark Content62                                                       |

| 4-1  | Pin List, Sorted by Socket Name65                                    |

| 4-2  | Pin List, Sorted by land Number                                    |

|------|--------------------------------------------------------------------|

| 5-1  | Signal Definitions 105                                             |

| 6-1  | Processor Thermal Specifications 112                               |

| 6-2  | 130W TDP Processor Thermal Profile Table                           |

| 6-3  | 105W TDP Processor Thermal Profile Table115                        |

| 6-4  | 95W TDP Processor Thermal Profile Table                            |

| 6-5  | Summary of Processor-specific PECI Commands 122                    |

| 6-6  | GetTemp() Response Definition 126                                  |

| 6-7  | PCIConfigRd() Response Definition 127                              |

| 6-8  | PCIConfigWr() Response Definition 129                              |

| 6-9  | Mailbox Command Summary 129                                        |

| 6-10 | Counter Definition                                                 |

| 6-11 | ACPI T-state Duty Cycle Definition                                 |

| 6-12 | MbxSend() Response Definition 135                                  |

| 6-13 | MbxGet() Response Definition 136                                   |

| 6-14 | Domain ID Definition                                               |

| 6-15 | Multi-Domain Command Code Reference 138                            |

| 6-16 | Completion Code Pass/Fail Mask                                     |

| 6-17 | Device Specific Completion Code (CC) Definition                    |

| 6-18 | Originator Response Guidelines 140                                 |

| 6-19 | Error Codes and Descriptions                                       |

| 6-20 | PECI Client Response During Power-Up (During 'Data Not Ready') 141 |

| 6-21 | Power Impact of PECI Commands vs. C-states 143                     |

| 6-22 | PECI Client Response During S1 143                                 |

| 7-1  | Processor C-State Power Specifications 146                         |

| 7-2  | Read Byte SMBus Packet 149                                         |

| 7-3  | Write Byte SMBus Packet 149                                        |

| 7-4  | Memory Device SMBus Addressing 150                                 |

| 7-5  | 128-Byte ROM Checksum Values 172                                   |

# **Revision History**

| Document<br>Number | Revision<br>Number | Description    | Date       |

|--------------------|--------------------|----------------|------------|

| 325119             | 001                | Public release | April 2011 |

§

# **1** Introduction

The Intel<sup>®</sup> Xeon<sup>®</sup> Processor E7-8800/4800/2800 Product Families are a nextgeneration Intel<sup>®</sup> Xeon<sup>®</sup> multi-core MP family processor. The processor uses Intel<sup>®</sup> QuickPath Interconnect (Intel<sup>®</sup> QPI) technology, implementing up to four high-speed serial point-to-point links. It is optimized for MP configurations targeted at enterprise and technical computing applications, delivering server-class RAS and performance.

Intel Xeon Processor E7-8800/4800/2800 Product Families are multi-core processors, based on 32-nm process technology. The processors feature Intel QuickPath Interconnect point-to-point links capable of up to 6.4 GT/s, up to 30 MB of shared cache, and an integrated memory controller. The processors support all the existing Streaming SIMD Extensions 2 (SSE2), Streaming SIMD Extensions 3 (SSE3) and Streaming SIMD Extensions 4 (SSE4). The processors support several Advanced Technologies: Execute Disable Bit, Intel<sup>®</sup> 64 technology, Enhanced Intel SpeedStep<sup>®</sup> technology, Intel<sup>®</sup> Virtualization technology (Intel<sup>®</sup> VT), and Simultaneous Multi-Threading.

| Feature                    | Intel <sup>®</sup> Xeon <sup>®</sup> Processor E7-8800/4800/2800 Product Families                                                               |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Cache Sizes                | Instruction Cache (L1) = 32 KB/core (I) and 16 KB/core (D)<br>Data Cache (L2) = 256 KB/core<br>Last Level Cache (L3) = 30 MB shared among cores |

| Data Transfer Rate         | Up to four full-width Intel QuickPath Interconnect links, up to 6.4 GT/s in each direction                                                      |

| Multi-Core Support         | Up to 10 cores per processor                                                                                                                    |

| Multiple Processor Support | Dependent on SKU, and supporting silicon. Minimum of two CPUs.                                                                                  |

| Package                    | 1567-land FCLGA                                                                                                                                 |

# 1.1 Terminology

A '\_N' after a signal name refers to an active low signal, indicating that a signal is in the asserted state when driven to a low level. For example, when RESET\_N is low (that is, when RESET\_N is asserted), a reset has been requested. Conversely, when TCK is high (that is, when TCK is asserted), a test clock request has occurred.

- Enhanced Intel SpeedStep technology Enhanced Intel SpeedStep technology allows the O/S to reduce power consumption when performance is not needed.

- **Eye Definitions** The eye at any point along the data channel is defined to be the creation of overlapping of a large number of UI of the data signal and timing width measured with regards to the edges of a separate clock signal at any other point. Each differential signal pair by combining the D+ and D- signals produces a signal eye. A \_DN and \_DP after a signal name refers to a differential pair.

- FCLGA-1567 The Intel Xeon Processor E7-8800/4800/2800 Product Families are available in a Flip-Chip Land Grid Array (FC-LGA) package, consisting of 10 processor cores mounted on a pinned substrate with an integrated heat spreader (IHS).

- **Functional Operation** Refers to the normal operating conditions in which all processor specifications, including DC, AC, system bus, signal quality, mechanical, and thermal, are satisfied.

- **Integrated Heat Spreader (IHS)** A component of the processor package used to enhance the thermal performance of the package. Component thermal solutions interface with the processor at the IHS surface.

- Intel<sup>®</sup> QuickPath Interconnect (Intel<sup>®</sup> QPI) Intel QuickPath Interconnect is a cache-coherent, links-based interconnect specification for Intel<sup>®</sup> processor, chipset, and I/O bridge components.

- Jitter Any timing variation of a transition edge or edges from the defined UI.

- **MP** Multi-processor system consisting of more than two processors.

- **OEM** Original Equipment Manufacturer.

- Processor Information ROM (PIROM) A memory device located on the processor and accessible via the System Management Bus (SMBus) which contains information regarding the processor's features. This device is shared with the Scratch EEPROM, is programmed during manufacturing, and is write-protected.

- Scratch EEPROM (Electrically Erasable, Programmable Read-Only Memory) — A memory device located on the processor and addressable via the SMBus which can be used by the OEM to store information useful for system management.

- SMBus System Management Bus. A two-wire interface through which simple system and power management related devices can communicate with the rest of the system. It is based on the principals of the operation of the I<sup>2</sup>C\* two-wire serial bus developed by Phillips Semiconductor. SMBus is a subset of the I<sup>2</sup>C bus/protocol developed by Intel. Implementations of the I<sup>2</sup>C bus/protocol or the SMBus bus/ protocol may require licensing from various entities, including, but not restricted to, Philips Electronics N.V. and North American Philips Corporation.

- Storage Conditions Refers to a non-operational state. The processor may be

installed in a platform, in a tray, or loose. Processors may be sealed in packaging or

exposed to free air. Under these conditions, processor pins should not be connected

to any supply voltages, have any I/Os biased, or receive any clocks.

- Intel<sup>®</sup> Xeon<sup>®</sup> Processor E7-8800/4800/2800 Product Families The entire product, including processor core, die, substrate and integrated heat spreader (IHS).

- Unit Interval (UI) Intel QPI signaling convention is binary and unidirectional. In this binary signaling, one bit is sent for every edge of the forwarded clock, whether it be a rising edge or a falling edge. If a number of edges are collected at instances  $t_1$ ,  $t_2$ ,  $t_n$ ,...,  $t_k$  then the UI at instance "n" is defined as:

UI  $_{n} = t_{n} - t_{n-1}$

# **1.2** References

Material and concepts available in the following documents may be beneficial when reading this document:

### Table 1-1. References

| Document                                                                                                     | Location   | Notes |

|--------------------------------------------------------------------------------------------------------------|------------|-------|

| Intel <sup>®</sup> Xeon <sup>®</sup> Processor E7-8800/4800/2800 Product Families<br>Datasheet Volume 2 of 2 | 325120     | 1     |

| AP-485, Intel <sup>®</sup> Processor Identification and the CPUID Instruction                                | 241618     | 1     |

| Intel <sup>®</sup> 64 and IA-32 Architecture Software Developer's Manual                                     |            | 1     |

| Volume 1: Basic Architecture                                                                                 | 253665     |       |

| Volume 2A: Instruction Set Reference, A-M                                                                    | 253666     |       |

| Volume 2B: Instruction Set Reference, N-Z                                                                    | 253667     |       |

| Volume 3A: System Programming Guide, Part 1                                                                  | 253668     |       |

| Volume 3B: Systems Programming Guide, Part 2                                                                 | 253669     |       |

| Intel® 64 and IA-32 Architectures Optimization Reference Manual                                              | 248966     | 1     |

| Intel <sup>®</sup> Virtualization Technology Specification for Directed I/O Architecture Specification       | D51397-001 | 1     |

| Voltage Regulator Module (VRM) and Enterprise Voltage Regulator-<br>Down (EVRD) 11.1 Design Guidelines       | 321736     | 1     |

#### Notes:

1. Document is available publicly at http://developer.intel.com.

# **1.3** State of Data

The data contained within this document is production data.

# **1.4 Statement of Volatility**

No Intel® Xeon® E7-8800/4800/2800 Product Families processors retain any end user data when powered down and/or when the parts are physically removed from the socket.

§

# **2** Electrical Specifications

The Intel Xeon Processor E7-8800/4800/2800 Product Families package pin electrical specification is outlined in this section. The Intel Xeon E7-8800/4800/2800 Product Families processor interfaces to other components of the platform via connections established at Intel<sup>®</sup> QuickPath Interconnect (Intel<sup>®</sup> QPI), Intel<sup>®</sup> Scalable Memory Interconnect (Intel<sup>®</sup> SMI), system management interfaces, power, reset, clock and debug signals. The electrical characteristics of all such signals, categorized per the I/O type, are documented in this section.

### 2.1 Processor Maximum Ratings

Table 2-1 specifies absolute maximum and minimum ratings. Within operational maximum and minimum limits, functionality and long-term reliability can be expected. Processor maximum ratings outlined in Table 2-1 are applicable for all Intel Xeon E7-8800/4800/2800 Product Families processor SKUs.

At conditions outside operational maximum ratings, but within absolute maximum and minimum ratings, neither functionality nor long-term reliability can be expected. If a device is returned to conditions within operational maximum and minimum ratings after having been subjected to conditions outside these limits, but within the absolute maximum and minimum ratings, the device may be functional, but with its lifetime degraded depending on exposure to conditions exceeding the functional operation condition limits.

At conditions exceeding absolute maximum and minimum ratings, neither functionality nor long-term reliability can be expected. Moreover, if a device is subjected to these conditions for any length of time, then when returned to conditions within the functional operating condition limits, it will either not function, or its reliability will be severely degraded.

Although the processor contains protective circuitry to resist damage from static electric discharge, precautions should always be taken to avoid high static voltages or electric fields.

| Symbol             | Parameter                                                     | Min   | Max   | Unit | Notes<br>1, 2 |  |

|--------------------|---------------------------------------------------------------|-------|-------|------|---------------|--|

| Vcc                | Processor core supply voltage with respect to VSS             | -0.3  | 1.42  | V    |               |  |

| V <sub>CACHE</sub> | Processor cache voltage with respect to VSS                   | -0.3  | 1.55  | V    |               |  |

| V <sub>REG</sub>   | Processor Analog Supply Voltage with respect to VSS           | -0.3  | 1.89  | V    |               |  |

| V <sub>IOC</sub>   | Processor Intel QPI I/O Supply<br>Voltage with respect to VSS | -0.3  | 1.55  | V    |               |  |

| V <sub>IOF</sub>   | Processor I/O Supply Voltage for SMI with respect to VSS      | -0.3  | 1.55  | V    |               |  |

| V <sub>CC33</sub>  | Processor 3.3V Supply Voltage with respect to VSS             | 3.135 | 3.465 | V    |               |  |

### Table 2-1. Processor Absolute Maximum Ratings (Sheet 1 of 2)

### Table 2-1. Processor Absolute Maximum Ratings (Sheet 2 of 2)

| Symbol               | Parameter                                                                   | Min           | Max           | Unit | Notes<br>1, 2 |

|----------------------|-----------------------------------------------------------------------------|---------------|---------------|------|---------------|

| V(ISENSE)            | Analog input voltage with respect to<br>Vss for sensing current consumption | -0.25         | 1.15          | V    |               |

| T <sub>CASE</sub>    | Processor case temperature                                                  | See Chapter 6 | See Chapter 6 |      |               |

| T <sub>STORAGE</sub> | Processor storage temperature                                               | -40           | 85            | °C   | 3, 4          |

Notes:

1. For functional operation, all processor electrical, signal quality, mechanical, and thermal specifications must be satisfied.

Excessive overshoot or undershoot on any signal will likely result in permanent damage to the processor.

Storage temperature is applicable to storage conditions only. In this scenario, the processor must not

Storage temperature is applicable to storage conditions only. In this scenario, the processor must not receive a clock, and no pins can be connected to a voltage bias. Storage within these limits will not affect the long-term reliability of the device. For functional operation, please refer to the processor case temperature specifications.

4. This rating applies to the processor and does not include any packaging or trays.

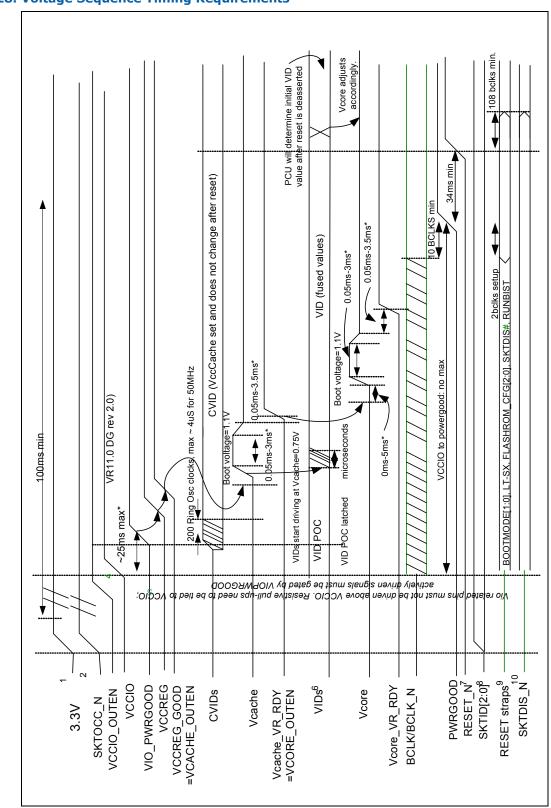

## 2.2 Socket Voltage Identification

The VID[7:0], CVID[7:1], and VIO\_VID[4:1] pins identify encoding that determine the voltage to be supplied by the VR to the socket Vcore, Vcache and VIO (the core, cache & system interface voltages for the Intel Xeon Processor E7-8800/4800/2800 Product Families processor) voltage regulators. The CoreVID and CacheVID specifications for the Intel Xeon Processor E7-8800/4800/2800 Product Families processors are defined by VR 11.1. VIO\_VID specifications for the Intel Xeon Processor E7-8800/4800/2800 Product Families processors are defined by VR 11.1.

For CoreVID and CacheVID, individual processor VID values may be calibrated during manufacturing such that two devices at the same core speed may have different default VID settings. Furthermore, any Intel Xeon Processor E7-8800/4800/2800 Product Families processor can drive different VID settings during normal operation. For VIO\_VID, all processors of a given stepping will have the same values.

The Voltage Identification (VID) specification for the Intel Xeon Processor E7-8800/ 4800/2800 Product Families processor is defined by the *Voltage Regulator Module* (*VRM*) and Enterprise Voltage Regulator-Down (EVRD) 11.1 Design Guidelines. The voltage set by the VID signals is the reference VR output voltage to be delivered to the processor Vcc pins. VID signals are CMOS push/pull drivers. Please refer to Table 2-24 for the DC specifications for these signals. A voltage range is provided in Table 2-5 and changes with frequency. The specifications have been set such that one voltage regulator can operate with all supported frequencies.

The Intel Xeon Processor E7-8800/4800/2800 Product Families processor uses eight voltage identification signals, VID[7:0], to support automatic selection of power supply voltages. Table 2-2 specifies the voltage level corresponding to the state of VID[7:0]. A '1' in this table refers to a high voltage level and a '0' refers to a low voltage level. If the processor socket is empty (SKTOCC# high), or the voltage regulation circuit cannot supply the voltage that is requested, the voltage regulator must disable itself. See the *Voltage Regulator Module (VRM) and Enterprise Voltage Regulator-Down (EVRD) 11.1 Design Guidelines* for further details.

The Intel Xeon Processor E7-8800/4800/2800 Product Families processor provides the ability to operate while transitioning to an adjacent VID and its associated processor core voltage (Vcc). This will represent a DC shift in the load line. It should be noted that a low-to-high or high-to-low voltage state change may result in as many VID transitions as necessary to reach the target core voltage. Transitions above the

maximum specified VID are not permitted. Table 2-5 includes VID step sizes and DC shift ranges. Minimum and maximum voltages must be maintained as shown in Table 2-6.

The VRM or EVRD utilized must be capable of regulating its output to the value defined by the new VID. DC specifications for dynamic VID transitions are included in Table 2-5 and Table 2-6, while AC specifications are included in Table 2-28. Refer to the *Voltage Regulator Module (VRM) and Enterprise Voltage Regulator-Down (EVRD) 11.1 Design Guidelines* for further details.

The VIO\_VID[4:1] pins identify encoding that determine the voltage to be supplied by the VR 11.1 to the socket Vio voltage regulators. In all cases, when reading from Table 2-2, assume VID7=0, VID6=1, VID5=0, and VID0=0. Note that all Intel Xeon Processor E7-8800/4800/2800 Product Families processor SKUs will have the same setting.

Power source characteristics must be guaranteed to be stable whenever the supply to the voltage regulator is stable.

| VID7 | VID6 | VID5 | VID4 | VID3 | VID2 | VID1 | VID0 | V <sub>CC_MAX</sub> |

|------|------|------|------|------|------|------|------|---------------------|

| 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | OFF                 |

| 0    | 0    | 0    | 0    | 0    | 0    | 0    | 1    | OFF                 |

| 0    | 0    | 0    | 0    | 0    | 0    | 1    | 0    | 1.60000             |

| 0    | 0    | 0    | 0    | 0    | 0    | 1    | 1    | 1.59375             |

| 0    | 0    | 0    | 0    | 0    | 1    | 0    | 0    | 1.58750             |

| 0    | 0    | 0    | 0    | 0    | 1    | 0    | 1    | 1.58125             |

| 0    | 0    | 0    | 0    | 0    | 1    | 1    | 0    | 1.57500             |

| 0    | 0    | 0    | 0    | 0    | 1    | 1    | 1    | 1.56875             |

| 0    | 0    | 0    | 0    | 1    | 0    | 0    | 0    | 1.56250             |

| 0    | 0    | 0    | 0    | 1    | 0    | 0    | 1    | 1.55625             |

| 0    | 0    | 0    | 0    | 1    | 0    | 1    | 0    | 1.55000             |

| 0    | 0    | 0    | 0    | 1    | 0    | 1    | 1    | 1.54375             |

| 0    | 0    | 0    | 0    | 1    | 1    | 0    | 0    | 1.53750             |

| 0    | 0    | 0    | 0    | 1    | 1    | 0    | 1    | 1.53125             |

| 0    | 0    | 0    | 0    | 1    | 1    | 1    | 0    | 1.52500             |

| 0    | 0    | 0    | 0    | 1    | 1    | 1    | 1    | 1.51875             |

| 0    | 0    | 0    | 1    | 0    | 0    | 0    | 0    | 1.51250             |

| 0    | 0    | 0    | 1    | 0    | 0    | 0    | 1    | 1.50625             |

| 0    | 0    | 0    | 1    | 0    | 0    | 1    | 0    | 1.50000             |

| 0    | 0    | 0    | 1    | 0    | 0    | 1    | 1    | 1.49375             |

| 0    | 0    | 0    | 1    | 0    | 1    | 0    | 0    | 1.48750             |

| 0    | 0    | 0    | 1    | 0    | 1    | 0    | 1    | 1.48125             |

| 0    | 0    | 0    | 1    | 0    | 1    | 1    | 0    | 1.47500             |

| 0    | 0    | 0    | 1    | 0    | 1    | 1    | 1    | 1.46875             |

| 0    | 0    | 0    | 1    | 1    | 0    | 0    | 0    | 1.46250             |

| 0    | 0    | 0    | 1    | 1    | 0    | 0    | 1    | 1.45625             |

| 0    | 0    | 0    | 1    | 1    | 0    | 1    | 0    | 1.45000             |

### Table 2-2. Voltage Identification Definition (Sheet 1 of 5)

| VID7 | VID6 | VID5 | VID4 | VID3 | VID2 | VID1 | VID0 | V <sub>CC_MAX</sub> |

|------|------|------|------|------|------|------|------|---------------------|

| 0    | 0    | 0    | 1    | 1    | 0    | 1    | 1    | 1.44375             |

| 0    | 0    | 0    | 1    | 1    | 1    | 0    | 0    | 1.43750             |

| 0    | 0    | 0    | 1    | 1    | 1    | 0    | 1    | 1.43125             |

| 0    | 0    | 0    | 1    | 1    | 1    | 1    | 0    | 1.42500             |

| 0    | 0    | 0    | 1    | 1    | 1    | 1    | 1    | 1.41875             |

| 0    | 0    | 1    | 0    | 0    | 0    | 0    | 0    | 1.41250             |

| 0    | 0    | 1    | 0    | 0    | 0    | 0    | 1    | 1.40625             |

| 0    | 0    | 1    | 0    | 0    | 0    | 1    | 0    | 1.40000             |

| 0    | 0    | 1    | 0    | 0    | 0    | 1    | 1    | 1.39375             |

| 0    | 0    | 1    | 0    | 0    | 1    | 0    | 0    | 1.38750             |

| 0    | 0    | 1    | 0    | 0    | 1    | 0    | 1    | 1.38125             |

| 0    | 0    | 1    | 0    | 0    | 1    | 1    | 0    | 1.37500             |

| 0    | 0    | 1    | 0    | 0    | 1    | 1    | 1    | 1.36875             |

| 0    | 0    | 1    | 0    | 1    | 0    | 0    | 0    | 1.36250             |

| 0    | 0    | 1    | 0    | 1    | 0    | 0    | 1    | 1.35625             |

| 0    | 0    | 1    | 0    | 1    | 0    | 1    | 0    | 1.35000             |

| 0    | 0    | 1    | 0    | 1    | 0    | 1    | 1    | 1.34375             |

| 0    | 0    | 1    | 0    | 1    | 1    | 0    | 0    | 1.33750             |

| 0    | 0    | 1    | 0    | 1    | 1    | 0    | 1    | 1.33125             |

| 0    | 0    | 1    | 0    | 1    | 1    | 1    | 0    | 1.32500             |

| 0    | 0    | 1    | 0    | 1    | 1    | 1    | 1    | 1.31875             |

| 0    | 0    | 1    | 1    | 0    | 0    | 0    | 0    | 1.31250             |

| 0    | 0    | 1    | 1    | 0    | 0    | 0    | 1    | 1.30625             |

| 0    | 0    | 1    | 1    | 0    | 0    | 1    | 0    | 1.30000             |

| 0    | 0    | 1    | 1    | 0    | 0    | 1    | 1    | 1.29375             |

| 0    | 0    | 1    | 1    | 0    | 1    | 0    | 0    | 1.28750             |

| 0    | 0    | 1    | 1    | 0    | 1    | 0    | 1    | 1.28125             |

| 0    | 0    | 1    | 1    | 0    | 1    | 1    | 0    | 1.27500             |

| 0    | 0    | 1    | 1    | 0    | 1    | 1    | 1    | 1.26875             |

| 0    | 0    | 1    | 1    | 1    | 0    | 0    | 0    | 1.26250             |

| 0    | 0    | 1    | 1    | 1    | 0    | 0    | 1    | 1.25625             |

| 0    | 0    | 1    | 1    | 1    | 0    | 1    | 0    | 1.25000             |

| 0    | 0    | 1    | 1    | 1    | 0    | 1    | 1    | 1.24375             |

| 0    | 0    | 1    | 1    | 1    | 1    | 0    | 0    | 1.23750             |

| 0    | 0    | 1    | 1    | 1    | 1    | 0    | 1    | 1.23125             |

| 0    | 0    | 1    | 1    | 1    | 1    | 1    | 0    | 1.22500             |

| 0    | 0    | 1    | 1    | 1    | 1    | 1    | 1    | 1.21875             |

| 0    | 1    | 0    | 0    | 0    | 0    | 0    | 0    | 1.21250             |

| 0    | 1    | 0    | 0    | 0    | 0    | 0    | 1    | 1.20625             |

| 0    | 1    | 0    | 0    | 0    | 0    | 1    | 0    | 1.20000             |

| 0    | 1    | 0    | 0    | 0    | 0    | 1    | 1    | 1.19375             |

| 0    | 1    | 0    | 0    | 0    | 1    | 0    | 0    | 1.18750             |

### Table 2-2.Voltage Identification Definition (Sheet 2 of 5)

| VID7 | VID6 | VID5 | VID4 | VID3 | VID2 | VID1 | VIDO | V <sub>CC_MAX</sub> |

|------|------|------|------|------|------|------|------|---------------------|

| 0    | 1    | 0    | 0    | 0    | 1    | 0    | 1    | 1.18125             |

| 0    | 1    | 0    | 0    | 0    | 1    | 1    | 0    | 1.17500             |

| 0    | 1    | 0    | 0    | 0    | 1    | 1    | 1    | 1.16875             |

| 0    | 1    | 0    | 0    | 1    | 0    | 0    | 0    | 1.16250             |

| 0    | 1    | 0    | 0    | 1    | 0    | 0    | 1    | 1.1562              |

| 0    | 1    | 0    | 0    | 1    | 0    | 1    | 0    | 1.1500              |

| 0    | 1    | 0    | 0    | 1    | 0    | 1    | 1    | 1.1437              |

| 0    | 1    | 0    | 0    | 1    | 1    | 0    | 0    | 1.1375              |

| 0    | 1    | 0    | 0    | 1    | 1    | 0    | 1    | 1.1312              |

| 0    | 1    | 0    | 0    | 1    | 1    | 1    | 0    | 1.1250              |

| 0    | 1    | 0    | 0    | 1    | 1    | 1    | 1    | 1.1187              |

| 0    | 1    | 0    | 1    | 0    | 0    | 0    | 0    | 1.1125              |

| 0    | 1    | 0    | 1    | 0    | 0    | 0    | 1    | 1.1062              |

| 0    | 1    | 0    | 1    | 0    | 0    | 1    | 0    | 1.1000              |

| 0    | 1    | 0    | 1    | 0    | 0    | 1    | 1    | 1.0937              |

| 0    | 1    | 0    | 1    | 0    | 1    | 0    | 0    | 1.0875              |

| 0    | 1    | 0    | 1    | 0    | 1    | 0    | 1    | 1.0812              |

| 0    | 1    | 0    | 1    | 0    | 1    | 1    | 0    | 1.0750              |

| 0    | 1    | 0    | 1    | 0    | 1    | 1    | 1    | 1.0687              |

| 0    | 1    | 0    | 1    | 1    | 0    | 0    | 0    | 1.0625              |

| 0    | 1    | 0    | 1    | 1    | 0    | 0    | 1    | 1.0562              |

| 0    | 1    | 0    | 1    | 1    | 0    | 1    | 0    | 1.0500              |

| 0    | 1    | 0    | 1    | 1    | 0    | 1    | 1    | 1.0437              |

| 0    | 1    | 0    | 1    | 1    | 1    | 0    | 0    | 1.0375              |

| 0    | 1    | 0    | 1    | 1    | 1    | 0    | 1    | 1.0312              |

| 0    | 1    | 0    | 1    | 1    | 1    | 1    | 0    | 1.0250              |

| 0    | 1    | 0    | 1    | 1    | 1    | 1    | 1    | 1.0187              |

| 0    | 1    | 1    | 0    | 0    | 0    | 0    | 0    | 1.0125              |

| 0    | 1    | 1    | 0    | 0    | 0    | 0    | 1    | 1.0062              |

| 0    | 1    | 1    | 0    | 0    | 0    | 1    | 0    | 1.0000              |

| 0    | 1    | 1    | 0    | 0    | 0    | 1    | 1    | 0.9937              |

| 0    | 1    | 1    | 0    | 0    | 1    | 0    | 0    | 0.9875              |

| 0    | 1    | 1    | 0    | 0    | 1    | 0    | 1    | 0.9812              |

| 0    | 1    | 1    | 0    | 0    | 1    | 1    | 0    | 0.9750              |

| 0    | 1    | 1    | 0    | 0    | 1    | 1    | 1    | 0.9687              |

| 0    | 1    | 1    | 0    | 1    | 0    | 0    | 0    | 0.9625              |

| 0    | 1    | 1    | 0    | 1    | 0    | 0    | 1    | 0.9562              |

| 0    | 1    | 1    | 0    | 1    | 0    | 1    | 0    | 0.9500              |

| 0    | 1    | 1    | 0    | 1    | 0    | 1    | 1    | 0.9437              |

| 0    | 1    | 1    | 0    | 1    | 1    | 0    | 0    | 0.9375              |

| 0    | 1    | 1    | 0    | 1    | 1    | 0    | 1    | 0.9312              |

| 0    | 1    | 1    | 0    | 1    | 1    | 1    | 0    | 0.9250              |

### Table 2-2. Voltage Identification Definition (Sheet 3 of 5)

| VID7 | VID6 | VID5 | VID4 | VID3 | VID2 | VID1 | VIDO | V <sub>CC_MAX</sub> |

|------|------|------|------|------|------|------|------|---------------------|

| 0    | 1    | 1    | 0    | 1    | 1    | 1    | 1    | 0.91875             |

| 0    | 1    | 1    | 1    | 0    | 0    | 0    | 0    | 0.91250             |

| 0    | 1    | 1    | 1    | 0    | 0    | 0    | 1    | 0.90625             |

| 0    | 1    | 1    | 1    | 0    | 0    | 1    | 0    | 0.90000             |

| 0    | 1    | 1    | 1    | 0    | 0    | 1    | 1    | 0.89375             |

| 0    | 1    | 1    | 1    | 0    | 1    | 0    | 0    | 0.88750             |

| 0    | 1    | 1    | 1    | 0    | 1    | 0    | 1    | 0.88125             |

| 0    | 1    | 1    | 1    | 0    | 1    | 1    | 0    | 0.87500             |

| 0    | 1    | 1    | 1    | 0    | 1    | 1    | 1    | 0.86875             |

| 0    | 1    | 1    | 1    | 1    | 0    | 0    | 0    | 0.86250             |

| 0    | 1    | 1    | 1    | 1    | 0    | 0    | 1    | 0.85625             |

| 0    | 1    | 1    | 1    | 1    | 0    | 1    | 0    | 0.85000             |

| 0    | 1    | 1    | 1    | 1    | 0    | 1    | 1    | 0.84375             |

| 0    | 1    | 1    | 1    | 1    | 1    | 0    | 0    | 0.83750             |

| 0    | 1    | 1    | 1    | 1    | 1    | 0    | 1    | 0.83125             |

| 0    | 1    | 1    | 1    | 1    | 1    | 1    | 0    | 0.82500             |

| 0    | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 0.81875             |

| 1    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0.81250             |

| 1    | 0    | 0    | 0    | 0    | 0    | 0    | 1    | 0.80625             |

| 1    | 0    | 0    | 0    | 0    | 0    | 1    | 0    | 0.80000             |

| 1    | 0    | 0    | 0    | 0    | 0    | 1    | 1    | 0.79375             |

| 1    | 0    | 0    | 0    | 0    | 1    | 0    | 0    | 0.78750             |

| 1    | 0    | 0    | 0    | 0    | 1    | 0    | 1    | 0.78125             |

| 1    | 0    | 0    | 0    | 0    | 1    | 1    | 0    | 0.77500             |

| 1    | 0    | 0    | 0    | 0    | 1    | 1    | 1    | 0.76875             |

| 1    | 0    | 0    | 0    | 1    | 0    | 0    | 0    | 0.76250             |

| 1    | 0    | 0    | 0    | 1    | 0    | 0    | 1    | 0.75625             |

| 1    | 0    | 0    | 0    | 1    | 0    | 1    | 0    | 0.75000             |

| 1    | 0    | 0    | 0    | 1    | 0    | 1    | 1    | 0.74375             |

| 1    | 0    | 0    | 0    | 1    | 1    | 0    | 0    | 0.73750             |

| 1    | 0    | 0    | 0    | 1    | 1    | 0    | 1    | 0.73125             |

| 1    | 0    | 0    | 0    | 1    | 1    | 1    | 0    | 0.72500             |

| 1    | 0    | 0    | 0    | 1    | 1    | 1    | 1    | 0.71875             |

| 1    | 0    | 0    | 1    | 0    | 0    | 0    | 0    | 0.71250             |

| 1    | 0    | 0    | 1    | 0    | 0    | 0    | 1    | 0.70625             |

| 1    | 0    | 0    | 1    | 0    | 0    | 1    | 0    | 0.70000             |

| 1    | 0    | 0    | 1    | 0    | 0    | 1    | 1    | 0.69375             |

| 1    | 0    | 0    | 1    | 0    | 1    | 0    | 0    | 0.68750             |

| 1    | 0    | 0    | 1    | 0    | 1    | 0    | 1    | 0.68125             |

| 1    | 0    | 0    | 1    | 0    | 1    | 1    | 0    | 0.67500             |

| 1    | 0    | 0    | 1    | 0    | 1    | 1    | 1    | 0.66875             |

| 1    | 0    | 0    | 1    | 1    | 0    | 0    | 0    | 0.66250             |

### Table 2-2.Voltage Identification Definition (Sheet 4 of 5)

| VID7 | VID6 | VID5 | VID4 | VID3 | VID2 | VID1 | VIDO | V <sub>CC_MAX</sub> |

|------|------|------|------|------|------|------|------|---------------------|

| 1    | 0    | 0    | 1    | 1    | 0    | 0    | 1    | 0.65625             |

| 1    | 0    | 0    | 1    | 1    | 0    | 1    | 0    | 0.65000             |

| 1    | 0    | 0    | 1    | 1    | 0    | 1    | 1    | 0.64375             |

| 1    | 0    | 0    | 1    | 1    | 1    | 0    | 0    | 0.63750             |

| 1    | 0    | 0    | 1    | 1    | 1    | 0    | 1    | 0.63125             |

| 1    | 0    | 0    | 1    | 1    | 1    | 1    | 0    | 0.62500             |

| 1    | 0    | 0    | 1    | 1    | 1    | 1    | 1    | 0.61875             |

| 1    | 0    | 1    | 0    | 0    | 0    | 0    | 0    | 0.61250             |

| 1    | 0    | 1    | 0    | 0    | 0    | 0    | 1    | 0.60625             |

| 1    | 0    | 1    | 0    | 0    | 0    | 1    | 0    | 0.60000             |

| 1    | 0    | 1    | 0    | 0    | 0    | 1    | 1    | 0.59375             |

| 1    | 0    | 1    | 0    | 0    | 1    | 0    | 0    | 0.58750             |

| 1    | 0    | 1    | 0    | 0    | 1    | 0    | 1    | 0.58125             |

| 1    | 0    | 1    | 0    | 0    | 1    | 1    | 0    | 0.57500             |

| 1    | 0    | 1    | 0    | 0    | 1    | 1    | 1    | 0.56875             |

| 1    | 0    | 1    | 0    | 1    | 0    | 0    | 0    | 0.56250             |

| 1    | 0    | 1    | 0    | 1    | 0    | 0    | 1    | 0.55625             |

| 1    | 0    | 1    | 0    | 1    | 0    | 1    | 0    | 0.55000             |

| 1    | 0    | 1    | 0    | 1    | 0    | 1    | 1    | 0.54375             |

| 1    | 0    | 1    | 0    | 1    | 1    | 0    | 0    | 0.53750             |

| 1    | 0    | 1    | 0    | 1    | 1    | 0    | 1    | 0.53125             |

| 1    | 0    | 1    | 0    | 1    | 1    | 1    | 0    | 0.52500             |

| 1    | 0    | 1    | 0    | 1    | 1    | 1    | 1    | 0.51875             |

| 1    | 0    | 1    | 1    | 0    | 0    | 0    | 0    | 0.51250             |

| 1    | 0    | 1    | 1    | 0    | 0    | 0    | 1    | 0.50625             |

| 1    | 0    | 1    | 1    | 0    | 0    | 1    | 0    | 0.50000             |

| 1    | 1    | 1    | 1    | 1    | 1    | 1    | 0    | OFF                 |

| 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    | OFF                 |

### Table 2-2.Voltage Identification Definition (Sheet 5 of 5)

#### Notes:

- 1. When the "11111111" VID pattern is observed, or when the SKTOCC# pin is deasserted, the voltage regulator output should be disabled.

- Shading denotes the expected VID range of the Intel Xeon Processor E7-8800/4800/2800 Product Families processor.

- The VID range includes VID transitions that may be initiated by thermal events, Extended HALT state transitions, higher C-States or Enhanced Intel® SpeedStep technology transitions. The Extended HALT state must be enabled for the processor to remain within its specifications

- 4. Once the VRM/EVRD is operating after power-up, if either the Output Enable signal is de-asserted or a specific VID off code is received, the VRM/EVRD must turn off its output (the output should go to high impedance) within 500 ms and latch off until power is cycled. Refer to Voltage Regulator Module (VRM) and Enterprise Voltage Regulator-Down (EVRD) 11.1 Design Guidelines.

### 2.3 Signal Groups

The signals are grouped by buffer type and similar characteristics, as listed in Table 2-3. The buffer type indicates which signaling technology and specifications apply to the signals. All the differential signals have On Die Termination (ODT) resistors. There are some signals that do not have ODT and need to be terminated on the board. The signals which have ODT are listed in Table 2-4.

### Table 2-3. Signal Groups (Sheet 1 of 2)

| Signal Group        | Туре                                | Signals <sup>1</sup>                                                                                  |

|---------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------|

| System Reference (  | Clock                               |                                                                                                       |

| Differential        | Differential Pair, HSTL             | SYSCLK_DP, SYSCLK_DN, SYSCLK_LAI_N,<br>SYSCLK_LAI                                                     |

| Intel® QPI Interfac | e Signal Groups                     |                                                                                                       |

| Differential        | SCiD 2 Input                        | QPI[3:0]_DRX_D[n/p][19:0],<br>QPI[3:0]_CLKRX_D[p/n]                                                   |

| Differential        | SCiD 2 Output                       | QPI[3:0]_DTX_D[n/p][19:0],<br>QPI[3:0]_CLKTX_D[p/n]                                                   |

| Intel® SMI Signals  |                                     |                                                                                                       |

| Differential        | Inputs                              | FBD0NBICLK[A/B][P/N]0<br>FBD1NBICLK[C/D][P/N]0                                                        |

| Differential        | Output                              | FBD0SBOCLK[A/B][P/N]0<br>FBD1SBOCLK[C/D][P/N]0                                                        |

| Differential        | Input                               | FBD0NBI[A/B][P/N][13:0]<br>FBD1NBI[C/D][P/N][13:0]                                                    |

| Differential        | Output                              | FBD0SBO[A/B][P/N][10:0], FBD1SBO[C/D][P/<br>N][10:0]                                                  |

| ТАР                 |                                     |                                                                                                       |

| Single ended        | GTL                                 | TCK, TDI,TMS, TRST_N                                                                                  |

| Single ended        | GTL-Open Drain                      | TDO                                                                                                   |

| PECI                |                                     |                                                                                                       |

| Single ended        | CMOS                                | PECI                                                                                                  |

| SMBus               |                                     |                                                                                                       |

| Single ended        | CMOS                                | SMBCLK, SMBDAT, SM_WP                                                                                 |

| SPD Bus             |                                     |                                                                                                       |

| Single ended        | CMOS I/OD                           | SPDCLK, SPDDAT                                                                                        |

| Strap Pins          |                                     |                                                                                                       |

| Single ended        | GTL                                 | BOOTMODE[1:0]                                                                                         |

| Single ended        | CMOS                                | SKTID[2:0]                                                                                            |

| Flash ROM Port      |                                     |                                                                                                       |

| Single ended        | GTL - OD                            | FLASHROM_CFG[2:0], FLASHROM_DATI<br>FLASHROM_CS[3:0]_N, FLASHROM_CLK,<br>FLASHROM_DATO, FLASHROM_WP_N |

| ERROR Bus           | ·                                   | ·                                                                                                     |

| Single ended        | GTL Input, GTL Open Drain<br>Output | ERROR[0]_N, ERROR[1]_N                                                                                |

| Power Up, RESETs    |                                     |                                                                                                       |

| Single ended        | CMOS Input                          | PWRGOOD, VIOPWRGOOD,                                                                                  |

| Single ended        | GTL Input                           | RUNBIST, RESET_N                                                                                      |

| Thermal             |                                     |                                                                                                       |

| Single ended        | GTL Input                           | Force_PR_N                                                                                            |

| Single ended        | GTL                                 | MEM_Throttle[1]_N,MEM_Throttle[0]_N                                                                   |

| Single ended        | GTL-Open Drain                      | PROCHOT_N, THERMTRIP_N                                                                                |

| Single ended        | CMOS - Open Drain                   | Thermalert_N                                                                                          |

### Table 2-3.Signal Groups (Sheet 2 of 2)

| Signal Group        | Type Signals <sup>1</sup> |                                                                                                             |  |  |  |

|---------------------|---------------------------|-------------------------------------------------------------------------------------------------------------|--|--|--|

| VID                 |                           |                                                                                                             |  |  |  |

| Single ended        | CMOS Output               | VID[7:0], CVID[7:1]                                                                                         |  |  |  |

| Single ended        | Open/Ground               | VIO_VID[4:1]                                                                                                |  |  |  |

| Voltage, and Voltag | e Regulator               | · ·                                                                                                         |  |  |  |

| Differential        | Power                     | ISENSE_DN, ISENSE_DP                                                                                        |  |  |  |

| Single ended        | Power                     | Vcc, VREG, VCACHE, VCACHESENSE,<br>VCC33,VCORESENSE, VIO, PSI_CACHE_N,PSI_N,<br>VSSCACHESENSE,VSSCORESENSE, |  |  |  |

| Debug               |                           | · ·                                                                                                         |  |  |  |

| Single ended        | GTL I/O-OD                | MBP[7:0]_N, PRDY_N,PREQ_N                                                                                   |  |  |  |

#### Notes:

1. See Chapter 5 for signal descriptions.

### Table 2-4. Signals with R<sub>TT</sub>

| Signals with RTT                                                                                                                                                                                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>QPI[3:0]R[P/N]Dat[19:0], QPI[5:4]R[P/N]CLK0, QPI[3:0]T[P/N]Dat[19:0],<br/>QPI[5:4]T[P/N]CLK0</li> </ul>                                                                                                           |

| <ul> <li>FBD0NBICLK[A/B][P/N]0, FBD1NBICLK[C/D][P/N]0, FBD0SBOCLK[A/B][P/N]0,<br/>FBD1SBOCLK[C/D][P/N]0, FBD0NBI[A/B][P/N][12:0], FBD1NBI[C/D][P/<br/>N][12:0], FBD0SB0[A/B][P/N][9:0], FBD1SB0[C/D][P/N][9:0].</li> </ul> |

## **2.4 Processor DC Specifications**

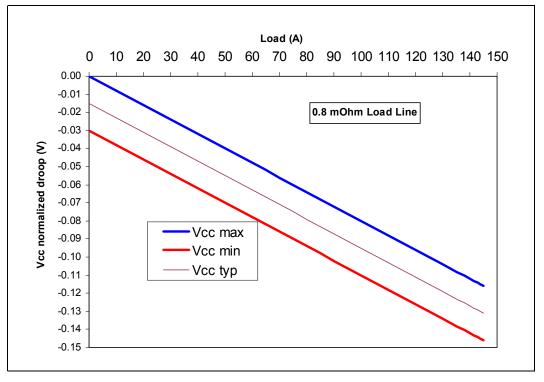

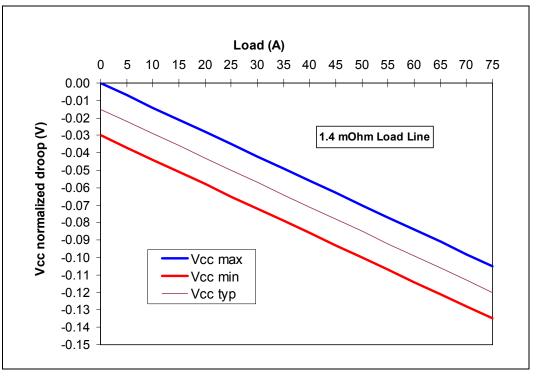

Voltage and current specifications are detailed in Table 2-5. For platform planning refer to Table 2-6, which provides Vcc static and transient tolerances.

Differential SYSCLK specifications are found in Table 2-26. Control Sideband and Test Access Port (TAP) are listed in Table 2-24.

Table 2-5 through Table 2-24 list the DC specifications for the processor and are valid only while meeting specifications for case temperature ( $T_{CASE}$  as specified in Chapter 6, "Thermal Specifications"), clock frequency, and input voltages. Care should be taken to read all notes associated with each parameter.

| Symbol                | Parameter                                          | Voltage<br>Plane | Min     | Тур     | Мах  | Unit | Notes 1 |

|-----------------------|----------------------------------------------------|------------------|---------|---------|------|------|---------|

| VID                   | VCore VID range                                    | N/A              | 0.60    |         | 1.35 | V    | 4,5     |

| Vcc                   | V <sub>CC</sub> for processor core<br>Launch - FMB |                  | See Tab | ole 2-6 |      | v    | 4,5,6   |

| Vcc LL                | Vcc Load Line                                      |                  |         | 0.8     |      | mΩ   |         |

| CVID                  | VCache VID range                                   |                  | 0.7     |         | 1.35 | V    | 4,5     |

| V <sub>CACHE</sub>    | Vcc for cache                                      |                  | See Tab | ole 2-7 |      | V    | 4,5,7   |

| V <sub>CACHE</sub> LL | V <sub>CACHE</sub> Load Line                       |                  |         | 1.4     |      | mΩ   |         |